AMD hat Einzelheiten zu den technischen Spezifikationen seines ersten ARM-basierten Prozessors für Microserver genannt. Die unter dem Codenamen „Seattle“ entwickelte Chipreihe Opteron A1100 basiert auf der ARMv8-Architektur. Sie bringt nicht nur 64-Bit-Kerne, sondern auch zusätzliche Enterprise-Features wie Unterstützung für Speicher mit ECC-Fehlerkorrektur.

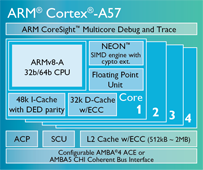

Die neuen 28-Nanometer-Prozessoren verfügen über vier oder acht Cortex-A57-Kerne und maximal 4 MByte L2-Cache. Ein Kernpaar teilt sich dabei 1 MByte Cache. Maximal werden 128 GByte ECC-Speicher unterstützt. Der Seattle-Chip mit acht Kernen besitzt zwei Speicherkanäle, die jeweils bis zu zwei Speichermodule mit einer Taktrate von 1,87 GHz unterstützen. Der integrierte Speicher-Controller erlaubt die Verwendung von DDR3- oder DDR4-RAM.

Außerdem bieten die Modelle der Opteron-A1100-Reihe Support für acht SATA-3-Ports mit Transferraten von jeweils 6 GBit/s, zwei 10GBase-KR-Ethernet-Anschlüsse und PCI Express 3.0 (x8). Ein dedizierter 1-Gigabit-Ethernet-Port zur Systemverwaltung (RGMII) ist ebenfalls vorhanden.

Ein Systemkontrollprozessor auf Basis von ARMs Cortex-A5-Design dient zur Überwachung der Stromzufuhr, Konfiguration des Systems und Initialisierung des Bootvorgangs. Zugleich agiert er als Service-Prozessor für Systemverwaltungsfunktionen. Ein kryptografischer Co-Prozessor soll zudem Ver- und Entschlüsselung beschleunigen.

AMD-Entwickler Sean White kündigte laut einem Bericht von Computerworld auf der Konferenz Hot Chip in Cupertino an, dass man darüber nachdenke, den Opteron-A1100-Chip an die Bedürfnisse von Großkunden anzupassen. Intel hatte seinen Kunden kürzlich ebenfalls diese Möglichkeit eingeräumt.

In diesem Jahr sollen mehrere ARM-basierte SoC-Prozessoren (System-on-a-Chip) auf den Markt kommen, die verschiedene Aufgaben in Rechenzentren übernehmen können – von der Handhabung von Server-Workloads bis zum Betrieb von Storage Arrays und virtuellen Netzwerken. Beispielsweise arbeiten auch Applied Micro, Broadcom, Cavium und Texas Instruments an solchen Chips. Ersteres hat Ende Juli bereits mit der Auslieferung begonnen.

Bisher kommen stromsparende Prozessoren auf ARM-Basis vor allem in Mobilgeräten wie Smartphones und Tablets zum Einsatz. Doch es gibt wachsendes Interesse, die energieeffizienten Chips auch in Servern einzusetzen. Sie würden sich vor allem für sogenannte Hyperscale-Workloads eignen, die besser durch Cluster mit tausenden leistungsschwächeren Prozessoren bewältigt werden können als durch eine geringe Zahl stärkerer Server-Chips. Das gilt etwa für die Bereitstellung statischer Elemente auf einer Website.

[mit Material von Nick Heath, ZDNet.com]

Tipp: Wie gut kennen Sie sich mit Prozessoren aus? Überprüfen Sie Ihr Wissen – mit dem Quiz auf silicon.de.

Neueste Kommentare

Noch keine Kommentare zu AMD enthüllt technische Details seiner Microserver-CPU Seattle

Kommentar hinzufügenVielen Dank für Ihren Kommentar.

Ihr Kommentar wurde gespeichert und wartet auf Moderation.